ARCHIVE ID

QL-GRS-2024-01

CATEGORY

QuantumLattice

STATUS

Active

CONDITION

Operational

GRIDSTEPS

Graduated Recursive Information Distribution Sequential Tiered Execution Processing System

Analysis

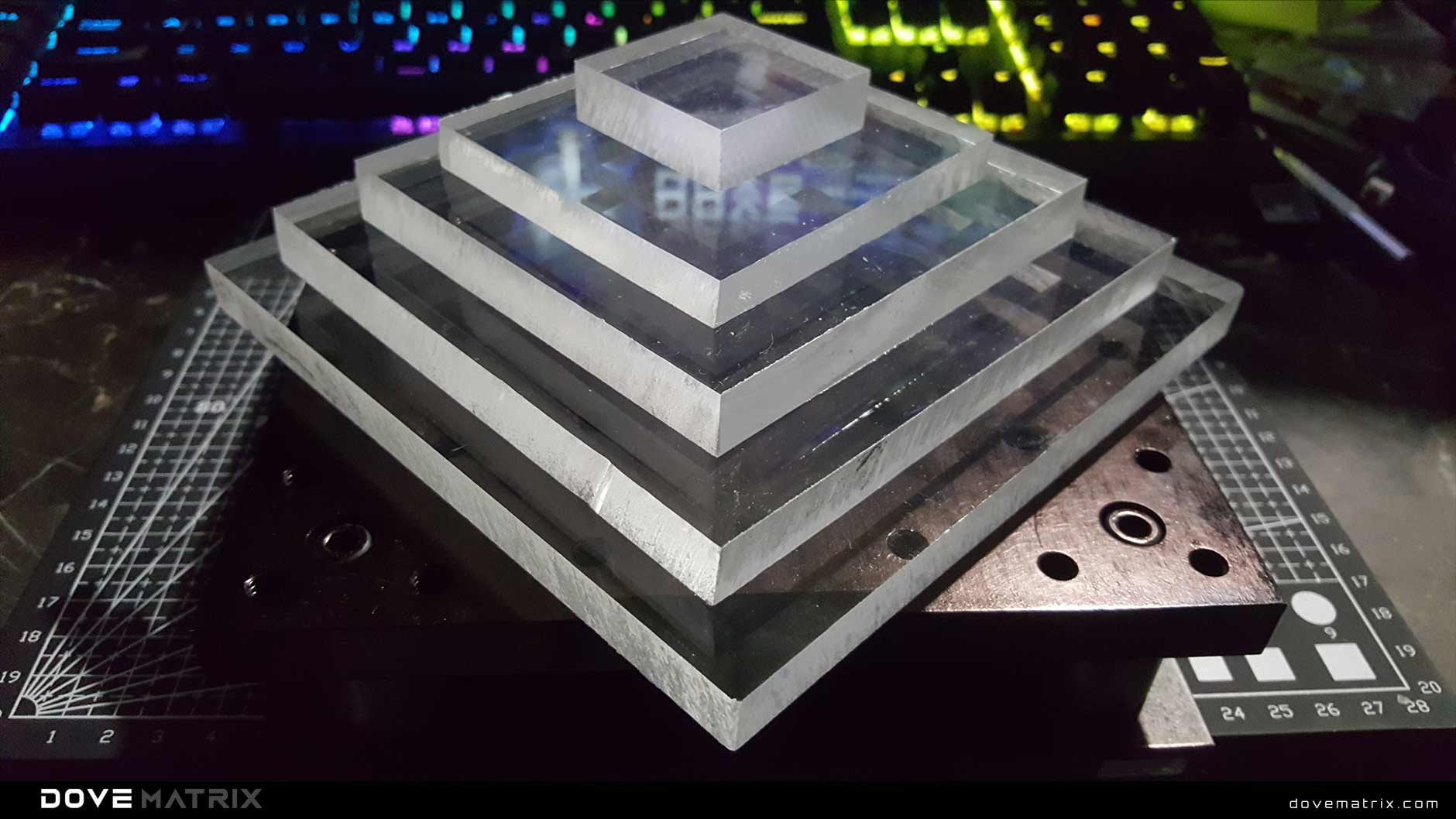

GRIDSTEPS Lattice Analysis Structure

Advanced visualization revealing data flow patterns and inter-tier communication pathways across the graduated lattice structure. Diagnostic overlays expose resolution progression and feedback loop connections throughout all processing levels.

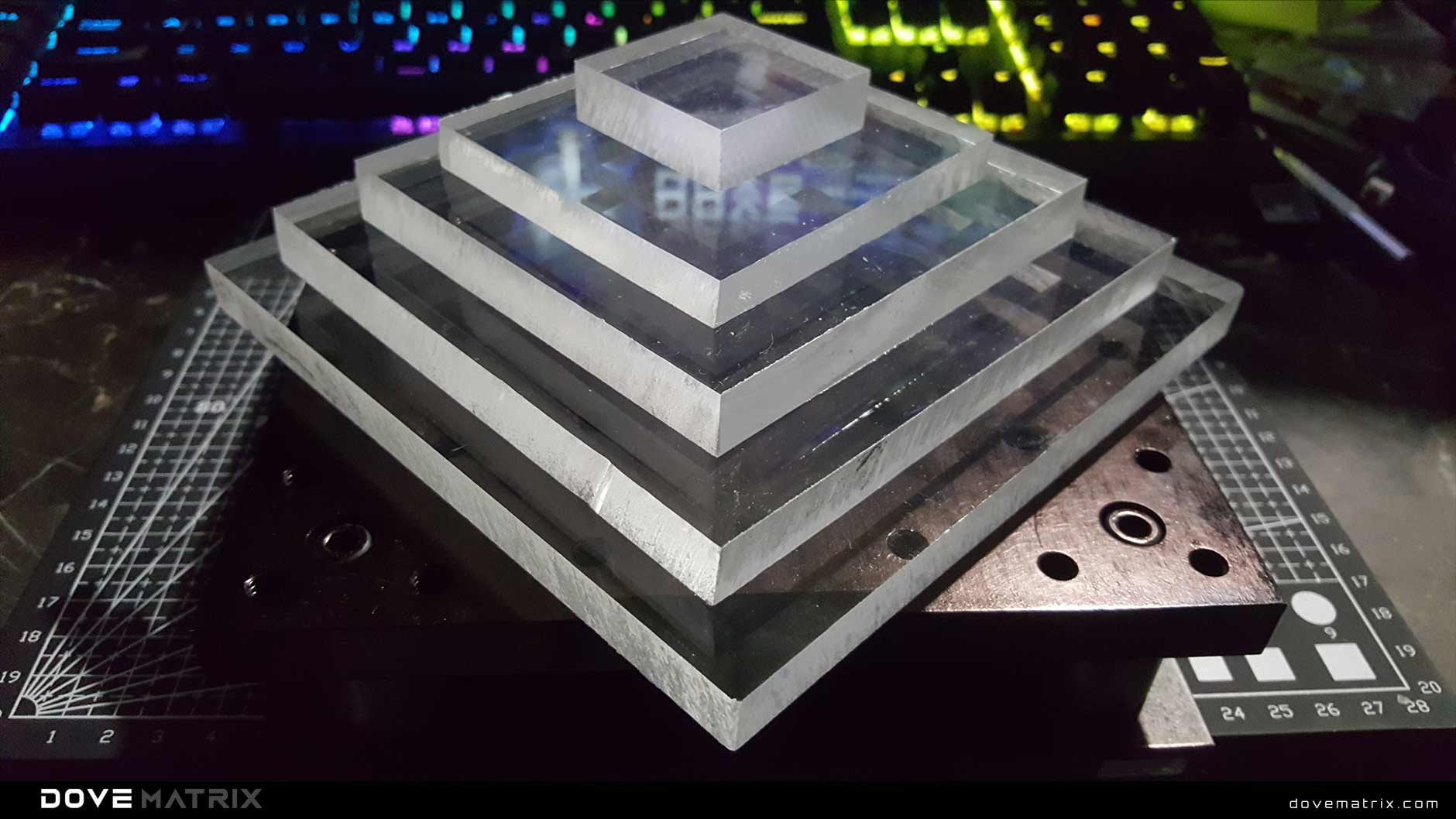

GRIDSTEPS Lattice Analysis Energy

Standard diagnostic mode displaying the stepped lattice progression system in its primary operational state. All tiered processing layers and sequential data flow pathways visible for baseline hierarchical analysis.

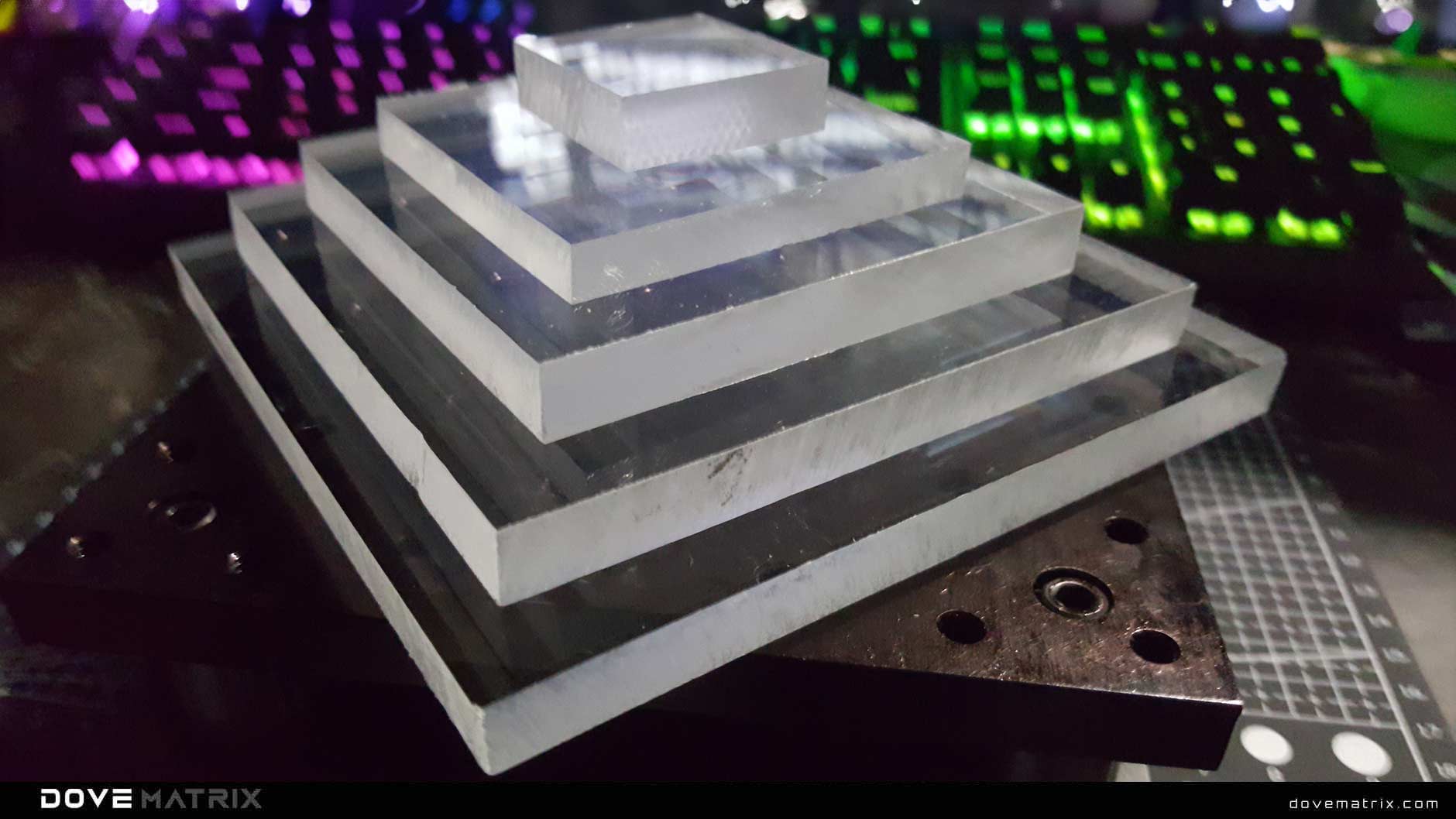

GRIDSTEPS Lattice Analysis Signal

Internal architecture analysis exposing inter-layer buffer systems, processing node arrangements, and bidirectional communication channels. Critical for examining hierarchical data transformation sequences and tier synchronization mechanisms.

Profile

Overview

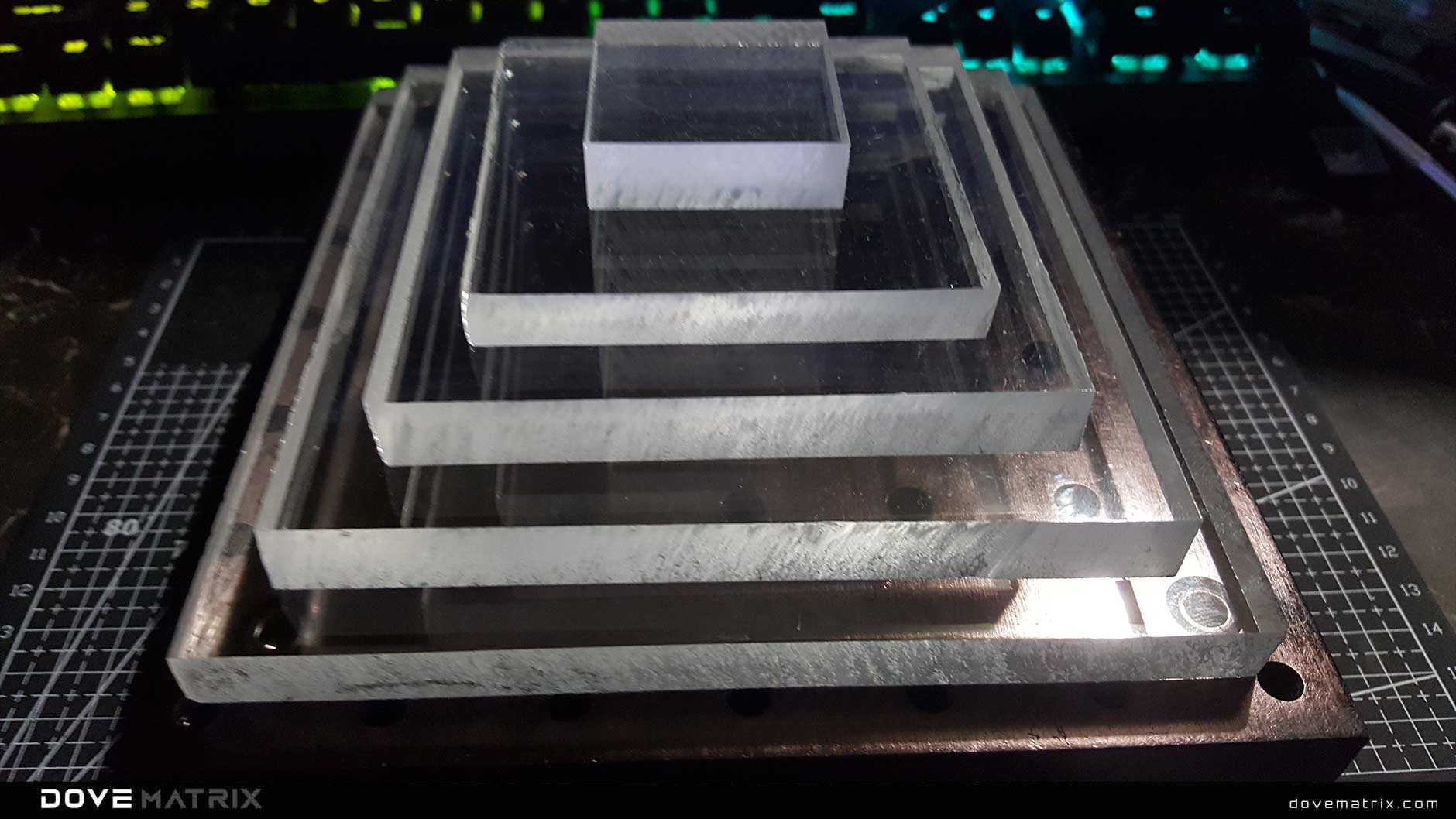

GRIDSTEPS is a graduated lattice framework implementing progressive information refinement through sequential tiered layers, where each processing stage transforms and enhances data before passing results to subsequent levels. Unlike flat processing architectures, GRIDSTEPS employs hierarchical organization mirroring biological neural structures, enabling complex emergent behaviors from repeated simple components.

The system utilizes multi-tiered architecture with cascading processing nodes featuring exponentially increasing resolution at each step. Core capabilities include hierarchical data transformation with automatic abstraction level adjustment, bidirectional feedback loops allowing higher tiers to dynamically influence lower-level parameters, asynchronous operation between layers through inter-tier buffer systems, and emergent pattern recognition that develops naturally from the tiered structure without explicit programming.

Architecture

GRIDSTEPS operational architecture implements a staged processing pipeline where raw input data enters at the base tier and undergoes progressive refinement through ascending layers. Each tier performs specialized transformations at increasing levels of abstraction, with lower layers handling raw signal processing and higher tiers managing semantic interpretation and decision logic.

Inter-layer communication employs buffered data channels maintaining flow continuity while enabling asynchronous tier operation at independent clock rates. The bidirectional feedback system allows higher-level processors to adjust lower-tier parameters in real-time, creating adaptive processing pipelines that self-optimize based on output quality metrics. Information flows upward through refinement stages and downward through control channels, establishing dynamic equilibrium where system behavior emerges from tier interactions rather than centralized control.

Behavior

Processing calibration requires precise tuning of inter-tier data transformation parameters and verification of feedback loop stability across all hierarchical levels. Primary calibration procedures include resolution scaling verification confirming appropriate abstraction progression between adjacent tiers, buffer synchronization ensuring data flow continuity without overflow conditions, feedback gain adjustment preventing oscillation in bidirectional control channels, and emergent behavior validation testing for expected pattern recognition capabilities.

Critical calibration parameters include processing latency maintained below 100µs per tier transition, buffer occupancy balanced between 40-60% to prevent both starvation and overflow, and feedback loop gain coefficients tuned to unity at DC while providing 20dB attenuation above the Nyquist frequency. Environmental considerations include thermal stability across processing nodes to prevent clock drift between asynchronous tiers and power supply regulation maintaining ±2% voltage tolerance to ensure consistent tier operation.